EUV 공정의 치명적 약점 드작위 패터닝 오류 '스토캐스틱 변동성' 급증

2나노 공정서 일일 690억 원 손실 우려

2나노 공정서 일일 690억 원 손실 우려

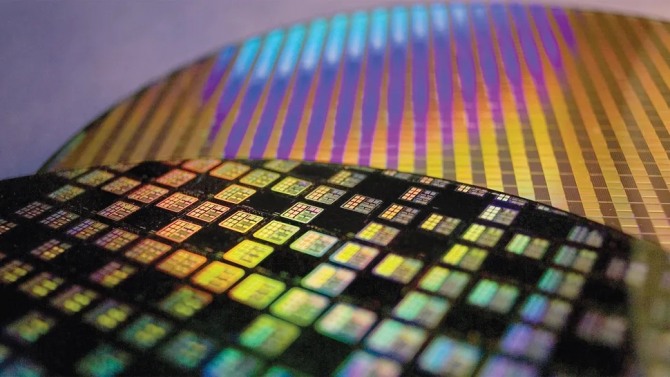

이미지 확대보기

이미지 확대보기28일(현지시각) 미국 반도체 측정 전문업체 프랙틸리아가 발표한 백서에 따르면, 극자외선(EUV) 리소그래피 기술 확산과 함께 이 같은 확률론적 오류가 첨단 공정의 양산 전환을 가로막는 주요 장벽으로 떠올랐다.

크리스 맥 프랙틸리아 최고기술책임자는 이 백서에서 "스토캐스틱 변동성이 첨단 공정 기술을 대량생산에 도입하는 데 수십억 달러 규모의 지연을 초래하고 있다"며 "기존 공정 제어 방식으로는 이러한 무작위 변동을 해결하는 데 한계가 있다"고 밝혔다.

◇ EUV 도입으로 5나노급 해상도 격차 발생

스토캐스틱 변동성은 반도체를 만들 때 사용하는 재료나 빛, 원자들이 예측할 수 없게 움직여서 회로 패턴이 불규칙하게 그려지는 현상이다. 예전에는 반도체 회로 패턴이 비교적 컸기 때문에 무작위 변동이 있어도 큰 문제가 되지 않았다. 하지만 EUV라는 새로운 기술로 훨씬 더 정밀하고 작은 회로를 만들 수 있게 되면서, 이제는 아주 작은 무작위 변동도 심각한 문제가 되고 있다.

프랙틸리아는 연구개발 단계에서 패턴화할 수 있는 피처 크기와 안정적으로 대량생산할 수 있는 피처 크기 사이의 차이를 '스토캐스틱 해상도 격차'로 정의했다. 현행 EUV 공정의 스토캐스틱 해상도 격차는 약 5나노미터 수준으로 분석됐다.

맥 CTO는 "고객들은 연구개발 단계에서 12나노미터 수준의 고밀도 피처를 성공적으로 구현했지만, 이를 양산에 적용하려 할 때 스토캐스틱 결함 때문에 목표 수율과 성능, 신뢰성 확보에 어려움을 겪고 있다"고 설명했다. 실제로 연구개발 단계에서는 최소 12나노미터 수준의 피처 크기까지 구현이 가능하나, 실제 양산에서는 통상 16~18나노미터 수준의 피처만 안정적으로 생산할 수 있는 것으로 나타났다.

이러한 격차는 웨이퍼 면적 낭비와 비용 증가, 제품 생산 지연 등으로 이어져 수조원 규모의 수익 손실을 일으키고 있다. 프랙틸리아 분석에 따르면 라인 변동성을 단 1나노미터만 줄여도 불량률이 최대 20배까지 개선될 수 있다. 최첨단 공정에서는 회로 패턴이 극도로 작아져서 아주 작은 변화만 있어도 회로 선이 끊어지거나 연결점이 빠지는 등 심각한 불량이 발생한다.

◇ TSMC 등 주요 업체서 솔루션 도입 확산

업계 관계자들은 EUV 공정에서 발생하는 전체 회로 그리기 오류의 50% 이상이 스토캐스틱 변동성에서 비롯된다고 보고 있다. 특히 2나노미터 이하 공정에서는 팹당 하루 약 5000만 달러(약 690억 원)의 매출 손실을 초래할 수 있어 반도체 산업 전반에 양산 지연을 유발하는 주요 원인으로 지목되고 있다.

맥 CTO는 "스토캐스틱 격차는 업계 전반에 영향을 미치는 문제"라며 "이를 최소화하고 제어할 수 있지만, 모든 해결의 출발점은 정확한 스토캐스틱 측정 기술 확보에서 시작된다"고 강조했다. 프랙틸리아는 이 문제 해결을 위해 정밀 측정과 확률 기반 공정 제어, 스토캐스틱 기반 설계 전략을 통합한 로드맵을 제시했다.

업계에서는 현재 세계 상위 5대 반도체 제조업체 중 4곳이 프랙틸리아의 스토캐스틱 측정 솔루션을 도입한 것으로 알려졌다. 특히 더욱 정밀한 차세대 EUV 장비가 본격 사용되는 시점에서 이런 해결책의 중요성이 더욱 커질 것으로 보인다.

박정한 글로벌이코노믹 기자 park@g-enews.com