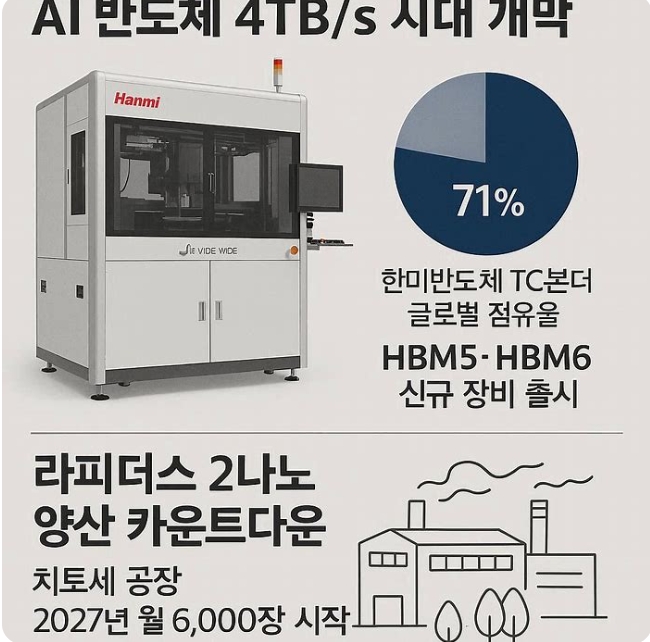

한미반도체 TC 본더 세계 점유율 71%, 올 하반기 HBM5·HBM6 겨냥 신형 장비 출시

라피더스 2나노 양산 초읽기…치토세 공장 2027년 월 6000장 출발, 1년 안에 2만5000장 목표

라피더스 2나노 양산 초읽기…치토세 공장 2027년 월 6000장 출발, 1년 안에 2만5000장 목표

이미지 확대보기

이미지 확대보기한미반도체가 HBM5 양산 장비를 세계 최초로 내놓고, 일본 라피더스는 2나노 칩 양산 계획을 확정했으며, 인텔은 TSMC 2나노 원가 부담에 직면했다.

한미반도체는 서울 코엑스 '2026 세미콘 코리아'에서 차세대 고대역폭메모리(HBM) HBM5·HBM6 양산용 '와이드 TC 본더'를 세계 최초로 공개했다고 Wccftech가 11일(현지시각) 보도했다. 같은 날 디지타임스는 일본 라피더스(Rapidus)가 2027년 하반기 2나노 칩 양산을 시작해 1년 안에 생산량을 4배로 끌어올리겠다는 사업 계획을 일본 경제산업성에 제출했다고 전했다. 톰스하드웨어도 같은 날 인텔 차세대 CPU '노바 레이크(Nova Lake)'의 TSMC 2나노(N2) 공정 다이 면적이 150㎟를 넘겨 제조 원가 상승이 불가피하다고 보도했다.

와이드 TC 본더, 하이브리드 본더 공백 파고들다

와이드 TC 본더는 올해 하반기 출시를 앞둔 차세대 HBM 생산 장비다. 하이브리드 본더(HB)가 기술 장벽에 막혀 상용화가 늦어지는 가운데, HBM4부터 HBM6까지 기존·차세대 규격을 모두 아우르는 대안으로 주목받고 있다. 플럭스(접합 보조제) 없이 칩 표면 산화막을 줄여 접합력을 높이면서 전체 두께를 낮추는 플럭스리스 본딩 방식이 핵심이다. HBM 다이 면적을 넓히면 실리콘관통전극(TSV)과 입출력(I/O) 채널을 안정하게 확장할 수 있어, 용량과 대역폭을 동시에 늘리면서 전력 효율도 함께 개선하는 구조다.

시장조사업체 테크인사이츠에 따르면 HBM용 TC 본더 시장은 2025~2030년 해마다 평균 13% 성장한다. 한미반도체는 이 시장에서 점유율 71.2%로 세계 1위를 지키고 있다. HBM5 규격은 입출력 레인 4096비트, 스택당 대역폭 4TB/s, 16단 적층으로 스택당 80GB 용량에 이르며, 엔비디아 '파인만(Feynman)' GPU와 AMD 인스팅트 MI500 플랫폼 탑재가 유력하다. HBM6는 대역폭을 8TB/s로 두 배 끌어올리고 적층 수를 20단까지 확대해 96~120GB를 구현한다. SK하이닉스·삼성전자의 차세대 HBM 로드맵이 이 규격과 맞물리는 만큼, 장비 선점이 곧 양산 주도권을 좌우한다.

라피더스, 일본 정부 올인 베팅 속 2나노 돌진

라피더스 사업 계획의 핵심은 2027년 하반기 홋카이도 치토세 공장에서 월 6000장 웨이퍼로 출발해 1년 안에 2만5000장까지 끌어올리는 것이다. 전공정(웨이퍼 가공)부터 후공정(다이싱·패키징)까지 한 공장에서 처리하는 통합 라인을 갖춘다. 200종 이상 장비를 동시에 가동하며 수율을 안정 궤도에 올려야 하는데, 교도통신은 이를 "가장 어려운 관문"이라고 짚었다.

일본 정부가 라피더스에 약속한 지원 규모는 누적 1조200억 엔(약 9조6400억 원)이고, 2026~2027년 1조 엔(약 9조4500억 원)을 추가로 투입한다. 혼다·캐논 등 20곳 이상이 새로 출자에 나섰고, 일본 3대 메가뱅크는 2027년 이후 최대 2조 엔(약 18조100억 원) 대출을 검토하고 있다. 라피더스 오리이 야스미쓰 엔지니어링센터장은 "칩렛 기술을 정교하게 다듬어 고성능 첨단 반도체에 도전하겠다"고 말했다.

삼성전자는 2나노 GAA(게이트올어라운드) 기반 '엑시노스 2600'을 양산 중이고 테슬라 AI칩도 2나노로 생산한다. 그러나 TSMC가 올해 2나노 양산을 본격화하며 애플·퀄컴을 확보한 데다, 라피더스까지 소량 맞춤형 시장을 파고들면 삼성전자 고객 확보 경쟁은 한층 치열해진다.

인텔 노바 레이크, 2나노 원가 부담의 신호탄

인텔 차세대 CPU 노바 레이크(코어 울트라 시리즈 4)의 다이 면적 유출이 2나노 공정 비용 상승의 실체를 수치로 드러냈다. TSMC N2 공정으로 제작한 컴퓨트 타일(코요테 코브 P코어 8개+아틱 울프 E코어 16개)은 110㎟를 넘기고, 144MB 대용량 캐시(bLLC)까지 포함하면 150㎟를 초과한다. 현행 애로 레이크(Arrow Lake) 컴퓨트 타일이 TSMC 3나노(N3B)에서 약 117㎟인 것과 견주면, 공정은 더 미세해졌는데 면적은 오히려 늘었다. N2는 N3B와 극자외선(EUV) 노광 레이어 수가 비슷하나 일부 핵심 레이어에 다중패터닝을 써서 원가가 올라간다.

인텔은 자사 애리조나 팹32의 18A 공정과 TSMC 대만 팹22의 N2를 함께 쓰는 이중 파운드리 전략으로 비용 부담을 나눈다. 노트북이 데스크톱 대비 7대 3으로 많이 팔리는 현실에서, 대다수 물량을 자체 공장에서 소화하면 TSMC 고비용 노출을 줄일 수 있다.

엔비디아 팀 코스타 산업·컴퓨팅 엔지니어링 총괄은 닛케이에 "TSMC에서 설계 시뮬레이션 연산을 최대 100배 가속하고 있다"며 "라피더스, 어드밴테스트 등 일본 기업과 협력 중"이라고 밝혔다. AI가 반도체 제조 공정 자체를 바꾸는 국면에 들어선 셈이다.

2나노 공정과 HBM5 이후 메모리가 만나는 2028~2029년이 AI 반도체 산업의 다음 변곡점이 될 것이라는 분석이 반도체 업계에서 나온다. 수율 확보 속도와 고객 다변화가 승패를 가를 핵심 변수다.

박정한 글로벌이코노믹 기자 park@g-enews.com