IMEC 로드맵 단독 입수… 2034년 CFET 거쳐 '2D FET'로 세대교체

구리 가고 루테늄 도입 배선 혁신… BSPDN·HBM 융합이 생존 분수령

구리 가고 루테늄 도입 배선 혁신… BSPDN·HBM 융합이 생존 분수령

이미지 확대보기

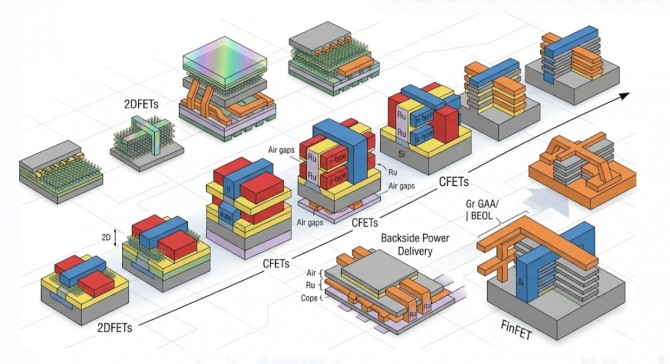

이미지 확대보기IT 전문매체 Wccftech는 지난 2일(현지 시각) IMEC이 발표한 '로직 디바이스 로드맵'을 인용해 반도체 산업이 2034년 1nm 장벽을 돌파하고, 2046년에는 0.2nm 이하의 2D FET(전계효과트랜지스터) 시대에 진입할 것이라고 보도했다. 이는 단순히 선폭을 줄이는 것을 넘어, 소재와 구조를 통째로 바꾸는 '거대한 과학 실험'의 영역으로 반도체 경쟁이 전환됐음을 의미한다.

2034년 0.7나노 문 연다… '수평' 가고 '수직' 쌓는 CFET의 등장

반도체 미세화의 핵심인 '로직 스케일링'은 최근 선형적 한계에 부딪혔다.

IMEC 분석에 따르면 지난 1998년부터 2010년까지 매년 50%씩 줄어들던 소자 면적은 2010년 이후 정체기에 접어들었다. IMEC은 이 한계를 돌파할 열쇠로 상보형 전계효과트랜지스터(CFET)를 지목했다.

현재 삼성전자가 세계 최초로 도입한 '나노시트(Nanosheet)' 방식은 2031년 1nm(A10) 공정까지 주력으로 쓰인다. 그러나 2034년 0.7nm(A7) 공정부터는 p채널과 n채널 나노시트를 위아래로 쌓는 CFET 구조가 필수적이다. CFET 구조를 도입하면 기존 방식보다 트랜지스터 밀도를 최대 80%까지 높일 수 있다.

IMEC은 이후 공정이 2036년 0.5nm(A5), 2040년 0.3nm(A3)로 속도를 낼 것으로 관측했다. 이는 인공지능(AI) 연산에 필요한 막대한 데이터를 처리하기 위해 더 좁은 면적에 더 많은 회로를 집어넣어야 하는 '고집적화' 요구를 반영한 결과다.

구리 시대 저물고 신소재 '루테늄' 급부상… 배선 혁신이 승부처

반도체 성능을 결정짓는 또 다른 축인 후공정(BEOL) 배선 기술에서도 대전환이 일어난다. 지금까지 회로를 연결하는 주력 소재는 구리(Cu)였지만, 선폭이 20nm 이하로 좁아지면 구리 특유의 저항값이 급증해 열 발생과 전력 손실이 심각해진다.

IMEC은 2031년 1nm(A10) 공정부터 구리를 대체할 루테늄(Ru) 소재를 본격 도입할 것으로 예고했다. 루테늄은 구리보다 얇게 만들어도 저항이 적고, 공기주머니(Air gap)를 형성해 신호 간섭을 최소화하는 '세미 다마신(Semi-damascene)' 공정에 유리하다.

증권가에서는 루테늄 관련 소재 및 장비 공급망을 선점하는 기업이 차세대 반도체 시장의 '숨은 승자'가 될 것으로 분석하고 있다.

또한 2037년 0.5nm 단계에서는 사파이어 기판 위에 백금 코발트 산화물(PtCoO2)을 사용하는 등 희귀 금속과 신소재가 반도체 가치를 결정하는 핵심 자원이 된다.

2043년 '2D FET' 시대… 원자 층 두께의 초저전력 반도체 탄생

로드맵의 종착지는 2043년 선보일 0.2nm(A2) 공정이다. 이때부터는 물리적 한계에 다다른 실리콘 대신 원자 한두 층 두께의 얇은 막인 2D 소재(이차원 물질)가 채널에 들어가는 '2D FET' 기술이 적용된다.전력 공급 방식도 가파르게 변한다.

2028년부터 2032년 사이에는 전력 조절기(IVR)를 메인보드가 아닌 칩 패키지 내부나 웨이퍼 뒷면에 직접 통합하는 '후면 전력 공급(Backside Power Delivery)' 기술이 표준으로 자리 잡는다. 이를 통해 48V(볼트)의 고전압을 칩 바로 아래에서 0.8V로 변압해 공급함으로써 전력 효율을 극대화한다.

삼성·SK 들고 있다면… 향후 5년 '이것' 보라

이번 IMEC 로드맵은 반도체 산업이 더 이상 '깎는 기술'만으로 버틸 수 없음을 명확히 보여준다. 투자자라면 향후 5년 내 다음 세 가지 변화를 주시하며 포트폴리오를 점검해야 한다.

첫째, 후면 전력 공급(BSPDN) 수율이다. 인텔의 '파워비아'나 삼성전자의 차세대 전력 공급 기술이 실제 양산 공정에서 얼마나 안정적인 수율을 확보하는지가 단기 승부처다.

둘째, 신소재 공급망 선점이다. 루테늄(Ru), 몰리브덴(Mo) 등 차세대 배선 소재 확보 여부가 기업 가치를 가를 것이다.

셋째, HBM과 로직의 3D 적층이다. AI 칩 성능은 이제 로직 단독이 아니라 메모리(DRAM)와 얼마나 가깝게, 수직으로 붙느냐에 달렸다. 삼성전자와 SK하이닉스의 3D 적층 기술 경쟁력을 눈여겨봐야 한다.

반도체 업계 관계자는 "0.2nm라는 꿈의 숫자를 향한 여정에서 소재와 구조를 혁신하지 못하는 기업은 도태될 수밖에 없다"며 "글로벌 파운드리 기업들의 기술 패권 경쟁은 이제 시작"이라고 진단했다.

김주원 글로벌이코노믹 기자 park@g-enews.com