수직 적층 기술로 통합 밀도 3배↑ 달성...'무어의 법칙' 한계 돌파

저온 제조 공정으로 기술적 난제 해결 웨어러블·IoT·의료 기기 아키텍처 제시

더 적은 공간에 더 많은 전력 집적...상업화 성공 시 반도체 판도 변화 예고

저온 제조 공정으로 기술적 난제 해결 웨어러블·IoT·의료 기기 아키텍처 제시

더 적은 공간에 더 많은 전력 집적...상업화 성공 시 반도체 판도 변화 예고

이미지 확대보기

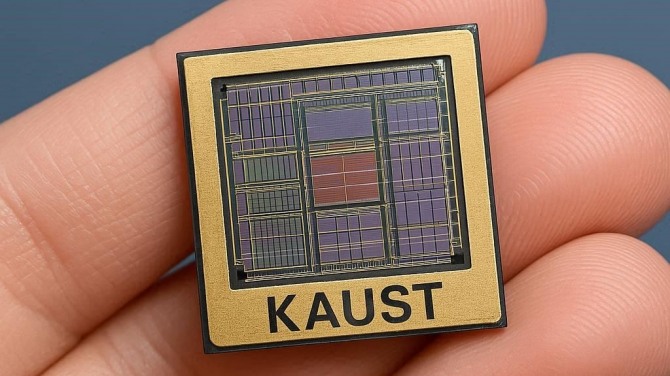

이미지 확대보기기존 2층에 불과했던 수직 적층 하이브리드 칩의 한계를 넘어선 세계 최초의 6층 하이브리드 CMOS(상보형 금속산화물 반도체) 마이크로칩을 개발했다고 과학 기술 전문매체 인터레스팅 엔지니어링이 18일(현지시각) 보도했다.

수직 확장으로 '무어의 법칙' 한계 돌파

이번 연구는 마이크로칩의 통합 밀도를 이전에는 불가능했던 수준으로 끌어올렸다는 점에서 의미가 크다. 수십 년간 반도체 산업을 지배해온 '무어의 법칙(트랜지스터 밀도가 2년마다 2배 증가)'은 트랜지스터 소형화의 물리적 한계와 생산 비용 증가로 인해 점차 한계에 부딪히고 있다.

인터레스팅 엔지니어링에 따르면 KAUST의 수석 연구원이자 박사후 연구원인 사라바난 유바라자 박사는 "마이크로칩 설계의 핵심은 더 적은 공간에 더 많은 전력을 집적하는 것"이라며 "이번 연구는 수직 확장과 기능 밀도 증가를 위한 청사진을 제시하며 오늘날의 한계를 훨씬 뛰어넘었다"고 설명했다. 연구진은 이번 성과가 단순한 기술적 업적을 넘어 스마트 전자 기기, 웨어러블 기기, 의료 기기를 위한 새로운 아키텍처를 제시한다고 강조했다.

두 개의 스택을 넘어서는 비결: 저온 공정 혁신

기존 칩 제조 방식에서 수직 적층은 △하부 층 손상을 야기하는 고온 공정 △여러 층을 완벽하게 정렬하는 기술적 난제 등으로 인해 층 수 증가에 제약이 있었다.

KAUST 연구진은 이러한 과제를 해결하기 위해 칩 제작 방식을 근본적으로 재검토했다. 모든 제조 단계를 화씨 302도(섭씨 150도) 이하, 대부분의 작업을 실온에 가까운 온도에서 수행하는 저온 공정을 개발한 것이다. 이는 새로운 층이 추가될 때 하부 층이 손상되는 것을 효과적으로 방지했다.

또한, 연구팀은 무기 물질(n형 산화인듐)과 유기 화합물로 만들어진 트랜지스터를 단일 구조로 결합하는 하이브리드 CMOS 아키텍처를 활용했다. 각 층의 제작 및 연결 방식도 개선하여 계면을 매끄럽고 정밀하게 정렬함으로써 층간 전기 신호의 효율적인 흐름을 확보했다.

최종적으로 개발된 칩은 6개의 활성층을 가지며, 이는 이전에 개발된 하이브리드 CMOS 칩보다 3배 더 많은 층수다. 이 칩은 안정적인 동작과 에너지 효율적인 논리 회로를 입증하며, 수직 적층 방식이 과열이나 전기적 간섭 없이 더 높은 성능을 제공할 수 있음을 증명했다.

전자제품의 미래를 바꿀 잠재력

이 새로운 칩 제조 방식은 다양한 기술 분야에 혁신을 가져올 것으로 기대된다.

유연하고 착용 가능한 전자 기기: 구부리거나 늘릴 수 있고, 직물에 통합될 수 있는 소형화된 센서 및 의료 기기 개발을 촉진할 수 있다.

사물 인터넷(IoT): 수백만 개의 작은 장치가 효율적으로 작동해야 하는 IoT 환경에서 최소한의 전력으로 강력한 컴퓨팅을 제공할 수 있다.

우주 및 환경 기술: 가벼운 무게와 높은 성능 덕분에 위성 및 원격 센서에 이상적인 솔루션이 될 수 있다.

연구는 아직 '개념 증명' 단계에 있으며, 상업화되기 위해서는 고온 안정성 강화 및 대량 생산 적합성 확보 등의 과제가 남아있다.

KAUST 팀은 앞으로 더 많은 층과 기능을 통합하고, 재료를 개선하며, 설계의 장기적 신뢰성을 높이는 연구를 계속할 계획이라고 밝혔다. 이번 혁신이 상업화에 성공한다면, 전자산업 전반에 걸쳐 엄청난 파급 효과를 가져올 것으로 전망된다.

이태준 글로벌이코노믹 기자 tjlee@g-enews.com