인텔 EMIB 기술로 패키징 한계 16mm까지 확장…엔비디아 '블랙웰' 정조준

'메모리 벽' 깬 샘 올트먼의 승부수, 한국 반도체 시장엔 위기인가 기회인가

'메모리 벽' 깬 샘 올트먼의 승부수, 한국 반도체 시장엔 위기인가 기회인가

이미지 확대보기

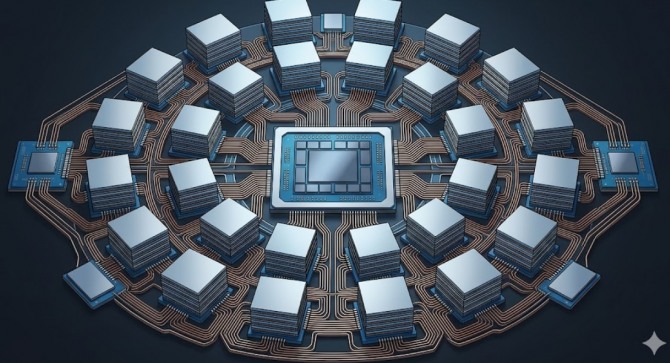

이미지 확대보기핵심은 고대역폭 메모리(HBM)의 물리적 연결 거리를 기존 6mm에서 16mm까지 대폭 확장하는 기술이다. 이를 통해 단일 칩에 최대 20개의 HBM 스택을 통합한다. 이번 특허는 단순히 칩 설계 방식을 바꾸는 차원을 넘어, 고성능 컴퓨팅(HPC) 시장에서 엔비디아의 독주 체제를 흔들 샘 올트먼의 강력한 승부수로 평가받는다.

'메모리 벽' 깬 20개의 HBM 스택

AI 칩 업계의 고질적인 난제는 '메모리 벽(Memory Wall)'이다. 연산 장치(GPU) 성능은 비약적으로 발전했지만, 이를 뒷받침할 메모리 대역폭은 물리적 배치 제약에 묶여 있었다. 현재 JEDEC 표준상 HBM은 연산 칩과 6mm 이내로 근접 배치돼야 한다. 이 제약 탓에 칩 패키징 내 수용 가능한 HBM 개수는 통상 4~8개 수준에 머물렀다.

오픈AI는 이 한계를 '브리지' 기술로 돌파한다. 인텔의 2.5D 패키징 기술인 EMIB(Embedded Multi-Interconnect Bridge)와 유사한 개념을 도입해, 연산 칩렛과 HBM 칩렛을 고속 로직 브리지로 연결한다. 신호 전달 거리가 16mm까지 늘어나자 칩 하나에 20개의 HBM 스택을 얹는 구조가 가능해졌다. 기존 대비 2.5배에서 5배까지 메모리 집적도를 끌어올린 셈이다.

엔비디아 대항마 노리는 패키징 혁신

이번 설계는 범용 GPU 중심의 컴퓨팅 시장에 큰 시사점을 던진다. 엔비디아는 블랙웰(Blackwell) 등 고성능 칩으로 시장을 장악하고 있으나, 패키징 효율과 메모리 용량 확대 경쟁은 이미 한계점에 도달했다는 분석이 지배적이다. 오픈AI가 자체 칩 개발을 통해 이 벽을 허문다면, 빅테크 기업들이 엔비디아 의존도를 낮출 강력한 유인책이 된다.

특히 UCIe(Universal Chiplet Interconnect Express) 표준을 준수한다는 점이 중요하다. 이는 특정 제조사의 기술에 종속되지 않고 다양한 칩렛을 조합할 수 있는 개방형 생태계를 지향한다. 인텔의 EMIB 솔루션이 접목되면 칩 제조 비용을 낮추면서도 확장성을 높이는 효율적인 생산 모델이 구축될 전망이다.

한국 반도체 기업, 위기인가 기회인가

이번 설계 변화는 한국 반도체 기업들에 양날의 검이다. HBM 수요가 폭발적으로 증가한다는 점은 SK하이닉스와 삼성전자에 호재다. 하지만 칩 패키징 설계가 파운드리와 팹리스의 경계를 허물고 브리지 기술을 중심으로 재편된다면, 기존의 수직계열화된 생산 방식도 변화가 불가피하다.

업계 전문가는 "이번 특허는 메모리 용량 부족 문제를 기술적으로 완벽히 타격하고 있다"며 "향후 AI 칩 경쟁은 칩 자체의 연산 속도보다, 얼마나 많은 메모리를 효율적으로 연결하느냐는 '패키징 생태계 주도권' 싸움으로 전개될 것"이라고 진단했다.

투자자·업계가 확인할 체크포인트

앞으로 시장 흐름을 읽기 위해 다음 세 가지 지표를 주목해야 한다.

첫째, HBM 공급량과 수율이다. 20개 스택을 안정적으로 패키징할 수 있는 수율이 확보되는가를 살펴야 한다. 20개 HBM 적층은 16mm 거리의 신호 무결성 유지와 고밀도 발열 제어가 핵심이다. 공정 복잡도가 기하급수적으로 늘어나는 만큼, 수율 확보 여부가 상용화 관건이다.

둘째, 패키징 기술 표준화다. 인텔 EMIB 등 브리지 기술이 다른 파운드리 업체로 얼마나 빠르게 확산하는가. 표준화 속도가 곧 칩 생산 단가와 직결된다.

셋째, 빅테크의 자체 칩 생산 시점이다. 오픈AI와 같은 기업들이 실제 상용 칩 생산을 위해 파운드리와 어떤 계약을 맺는지 확인해야 한다.

하드웨어의 물리적 한계를 새로운 패키징 기술로 돌파하려는 시도는 이미 시작됐다. 이제 승패는 설계도를 넘어 누가 더 빠르게 대량 양산 체제를 구축하느냐에 달려 있다.

김주원 글로벌이코노믹 기자 park@g-enews.com